40 www.xilinx.com SPI-4.2 Lite v4.3 User Guide

UG181 June 27, 2008

Chapter 2: Core Architecture

R

the slave clocking signals. The minimum frequency for all clocks is dependent on the

minimum frequency of the DCM.

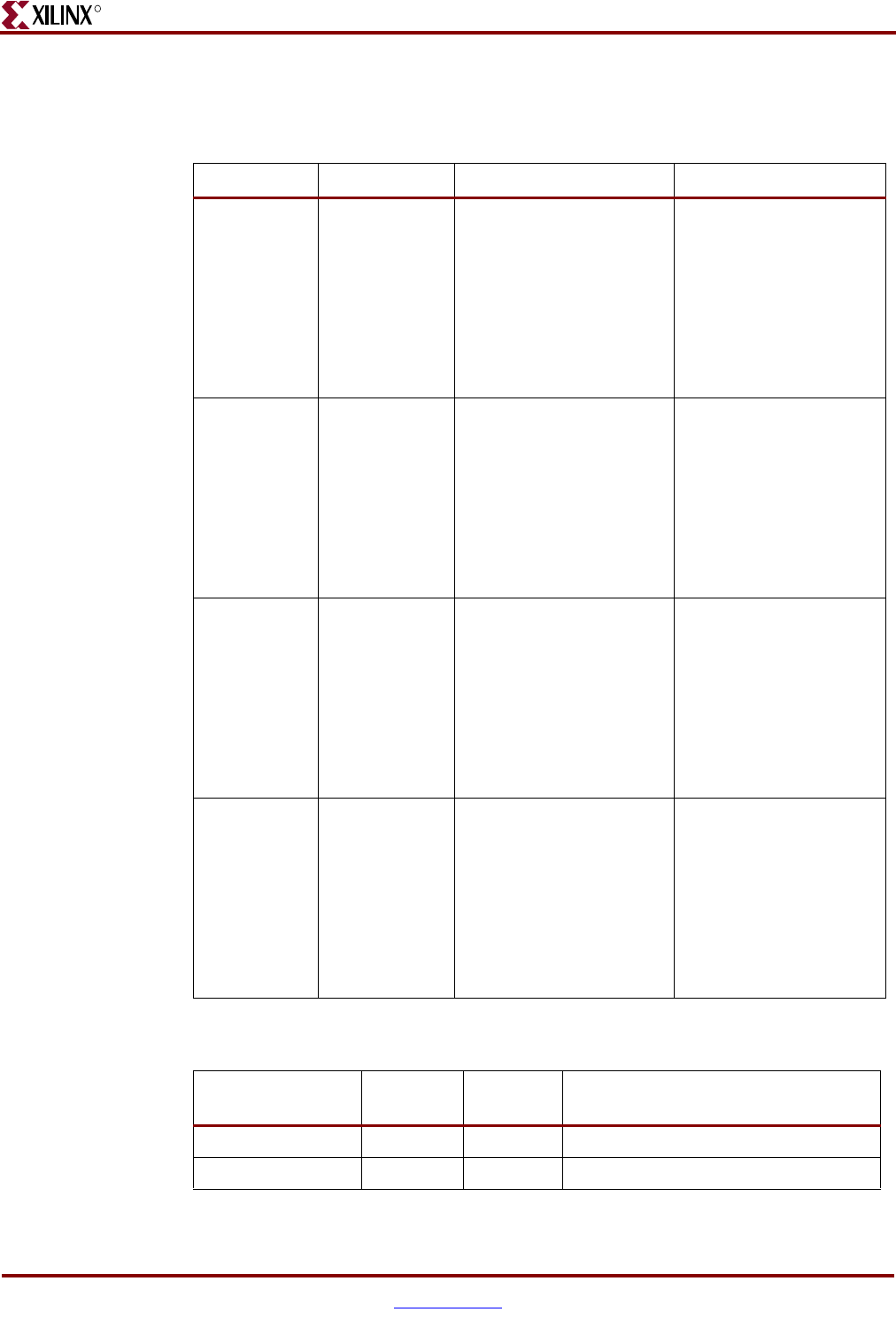

Table 2-16: Source Core Clocks: Master Configuration

Clock Pins Direction Description Max Freq.

SysClk_P

SysClk_N

Input

(differential)

SysClk: A The frequency of

TDClk is the same as SysClk.

It is recommended that

SysClk should be a low jitter

(<50ps) reference clock, as

any jitter present on the

SysClk input will appear on

the TDClk output.

Virtex-5: 275 MHz

Virtex-4: 190 MHz

Virtex-II Pro: 160 MHz

Virtex-II: 160 MHz

Spartan-3: 115 MHz

Spartan-3E: 90 MHz

Spartan-3A/3AN/3A DSP:

105 MHz

SysClk0_GP Output

(user interface)

SysClk0 General Purpose:

This clock is generated from

SysClk. It is used to clock the

Internal Source core logic.

Virtex-5: 275 MHz

Virtex-4: 190 MHz

Virtex-II Pro: 160 MHz

Virtex-II: 160 MHz

Spartan-3: 115 MHz

Spartan-3E: 90 MHz

Spartan-3A/3AN/3A DSP:

105 MHz

SysClk180_GP Output

(user interface)

SysClk180 General

Purpose: This clock is

generated from SysClk and

the inverted equivalent of

SysClk0_GP. It is used to

clock the internal Source

core’s logic.

Virtex-5: 275 MHz

Virtex-4: 190 MHz

Virtex-II Pro: 160 MHz

Virtex-II: 160 MHz

Spartan-3: 115 MHz

Spartan-3E: 90 MHz

Spartan-3A/3AN/3A DSP:

105 MHz

TSClk_GP Output

(user interface)

TSClk General Purpose:

This clock is generated from

TSClk. It is a quarter the

frequency of TDClk.

Virtex-5: 275 MHz

Virtex-4: 190 MHz

Virtex-II Pro: 160 MHz

Virtex-II: 160 MHz

Spartan-3: 115 MHz

Spartan-3E: 90 MHz

Spartan-3A/3AN/3A DSP:

105 MHz

Table 2-17: Source Core Clock Status Signals: Master Configuration

Signal Name Direction

Clock

Domain

Description

DCMReset_TDClk Input N/A Reset of TDClk DCM

Locked_TDClk Output N/A Locked status of TDClk DCM