3 - 2

3 MOTION DEDICATED PLC INSTRUCTION

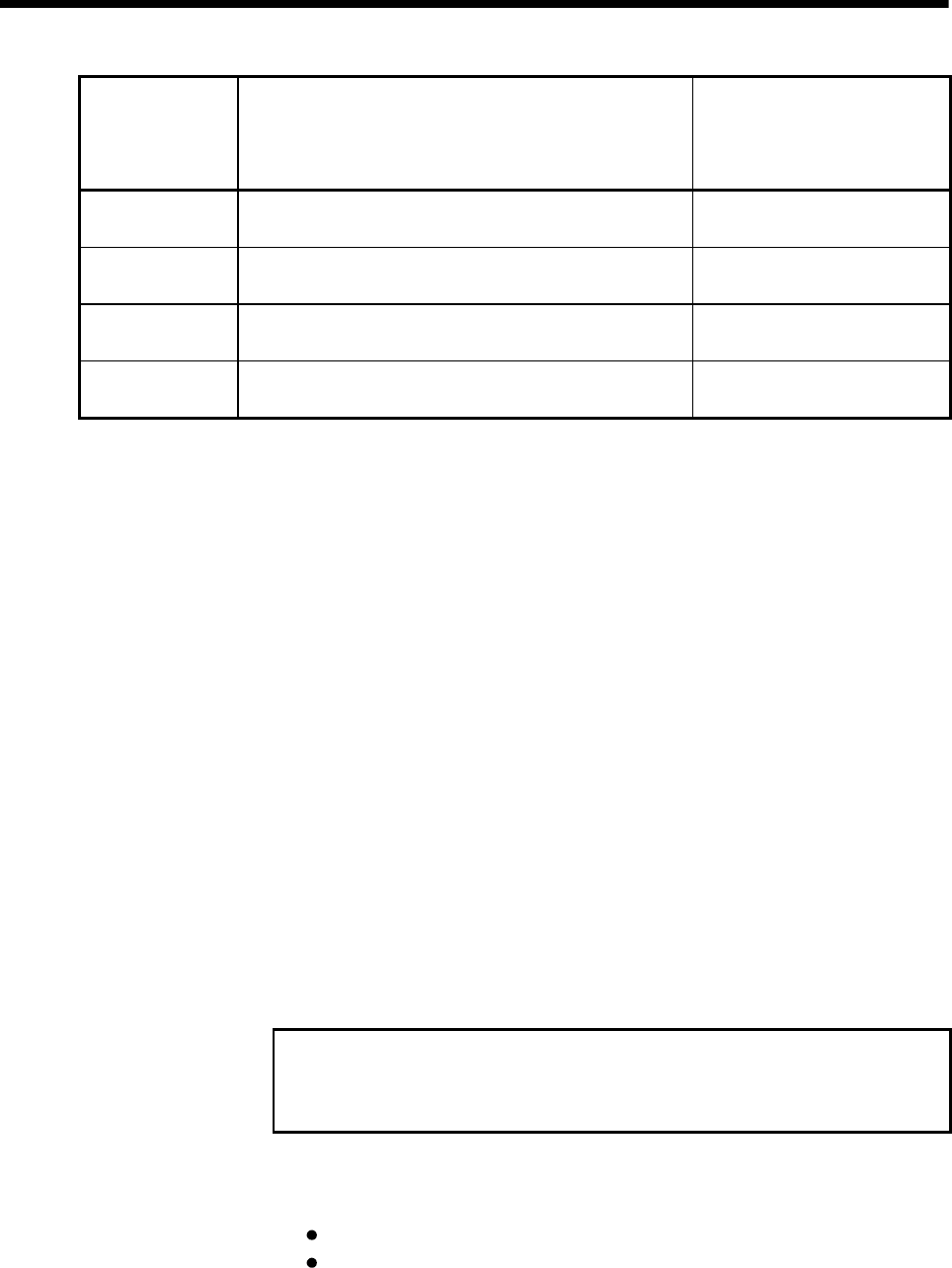

Shared CPU

memory address

( ) is decimal

address

Description

Example of the reading

(When target is the CPU No.2)

30H(48)

The lowest rank bit (30H(48)) toward executing instruction

from CPU No.1.

U3E1/G48.0

31H(49)

The lowest rank bit (31H(49)) toward executing instruction

from CPU No.2.

U3E1/G49.0

32H(50)

The lowest rank bit (32H(50)) toward executing instruction

from CPU No.3.

U3E1/G50.0

33H(51)

The lowest rank bit (33H(51)) toward executing instruction

from CPU No.4.

U3E1/G51.0

(b) "To self CPU high speed interrupt accept flag from CPUn" turn ON/OFF at

the executing instruction, when the Multiple CPU dedicated instructions are

executed to the same CPU from one PLC CPU.

Therefore, when each instruction is executed only once at approval the

executing condition, it is necessary to take an interlock by internal relay

(M10) and so on besides "To self CPU high speed interrupt accept flag from

CPUn".

(2) Execution of the Motion dedicated PLC instruction

(a) Motion dedicated PLC instruction can be executed with fixed cycle execute

type PLC and interrupt PLC. However, as for a complete device, the program

turned on according to fixed cycle executed type PLC and program type

(scan or low speed) executed interrupt PLC is different.

(b) One Motion CPU can be accepted up to 32 instructions simultaneously from

multiple other CPUs. If 33 instructions or more are executed Motion CPU

returns the complete status[4C08] error.

As Motion CPU can be accepted up to 32 instructions, number of

acceptable instructions changes according to number of CPUs included

Motion CPU. Calculation expression is shown below.

(Number of maximum acceptable instructions per one Motion CPU) =

32 – ( (Number of all CPUs) – 2 ) [Number of instructions]

(c) Local devices and file registers as program are written to device by END

processing. Do not use the devices below.

Each instruction complete device

D1 of S(P).DDRD instruction (The first device of the self CPU which

stored the reading data.)