BERT Technical Articles

GB1400 User Manual B-27

The simplest fixed pattern with a 50% transition density is again 11001100. The patterns in Table 1 that

stress noise margin by varying the balance of 1s and 0s also maintain a 50% transition density. Similarly,

patterns that stress the clock-recovery circuit by varying transition density should keep the 1s and 0s in

balance (see the following table).

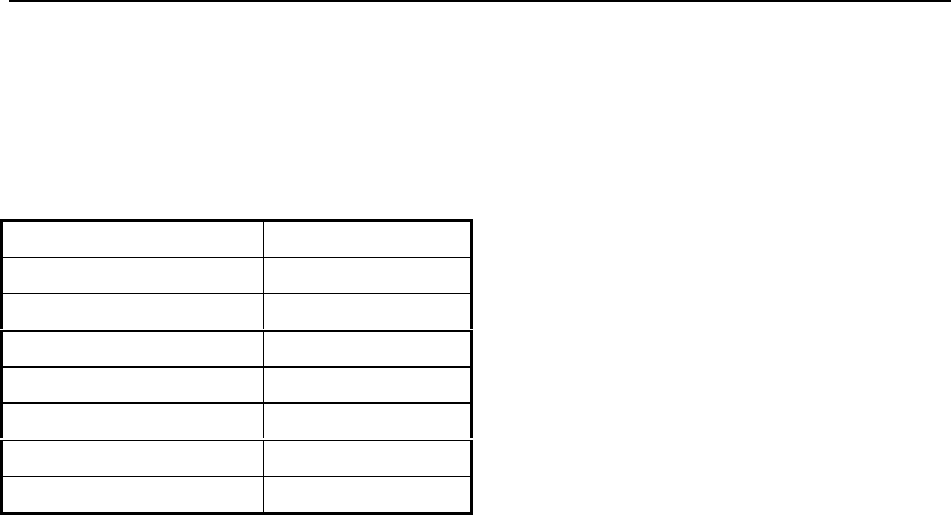

Table 2. Data patterns for clock recovery stressing

Pattern Transition density

1010101010101010 100%

1010110010101100 75%

1100110011001100 50% (normal)

11001110001100111000 40%

111000111000111000 33%

11100011100011110000 30%

1111000011110000 25%

As the transition density is increased or decreased from 50%, the clock-recovery circuit will fail and the

error rate will become significant. A well-designed clock recovery will typically tolerate transition

densities between 100% and 25% without causing errors.

Data Patterns Stored

Fixed patterns can also be designed to simulate valid line formats in telecommunications.

One such format is DS2, the third level in the North American digital hierarchy at 6.312 Mbits/s. The

DS2 frame is 1176 bits long, organized into 24 groups of 49 bits. The first bit in each group of 49 is a

framing bit or a control bit, and the rest are data bits. A BERT transmitter can generate such a pattern to

test terminal equipment that looks for the framing and control bits.

Fixed data patterns are stored in the BERT transmitter. User-defined patterns are stored in RAM, and

manufacturer-provided patterns are stored in ROM.

The BERT receiver must be programmed to produce the same data pattern as the transmitter. The receiver

synchronizes its pattern, H’, to the received data pattern, H, on the basis of error rate. If the error rate is

greater than some set level, say 10

-2

, H’ is shifted one bit by dropping a clock pulse. This continues until

the synchronization is achieved, as indicated by an error rate less than 10

-2

.

Another type of pattern, a psuedorandom bit sequence (PRBS), simulates live traffic. A PRBS has all of

the properties of a random sequence but is periodic. A fixed pattern could be programmed to produce a

PRBS, but a simple circuit can generate a pattern millions of bits long with only 20 to 30 bits of memory.

Common pattern lengths are N=2

7

-1, 2

15

-1, and 2

23

-1.

PRBS patterns can stress the noise margin and the clock recovery as fixed patterns do. But it is done

randomly, somewhat like live traffic. When averaged over the whole sequence, the number of 1s and 0s

almost equal (actually different by one), and transition density is 50%. Over a short term, though, the

averages can be very different, stressing both noise margin and clock recovery for periods of time.