Functional Overview

GB1400 User Manual 2-3

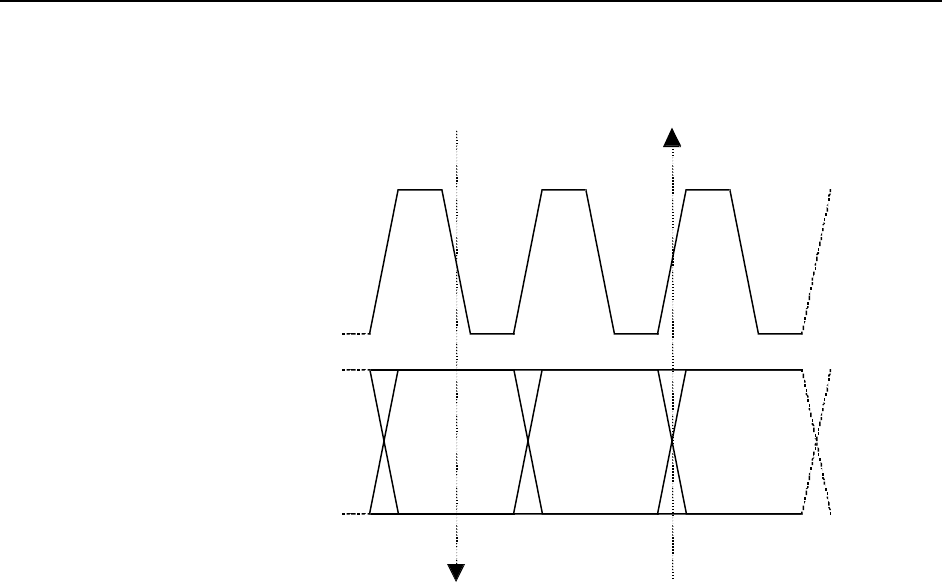

DATA

CLOCK

Falling edge of CLOCK

in middle of DATA "eye"

Rising edge of CLOCK Coin-

cident with DATA transitions

Figure 2-2. Nominal Generator NRZ Data and Clock Output

Waveforms

The nominal Generator clock/data phase relationship is fixed so that the falling

edges of the clock signal occur in the middle of bit time slots of the data signal.

The amplitude and baseline offset of the Generator's clock and data outputs are

adjustable to insure compatibility with a wide range of input circuit designs and

logic families including ECL, positive ECL, and GaAs.

The GB1400 Analyzer, also known as the receiver or "Rx", can terminate and

analyze the NRZ output of a digital device, module, or system being tested by the

GB1400 Generator or an equivalent signal source. The decision voltage or

threshold of the Analyzer DATA and CLOCK inputs can be adjusted to

accommodate different logic families. The Analyzer can also add a variable

amount of delay to the input data signal to accommodate different clock/data

phase relationships at the output of the device under test.

The primary measurements made by the GB1400 Analyzer are bit errors and bit

error rate.